# FlashRunner LAN 2.0 Next Generation

# High-Performance, Compact Standalone In-System Programmer

**User's Manual**

Revision 0.5 — Apr 2021

Copyright © 2018 SMH Technologies DC11261

#### We want your feedback!

SMH Technologies is always on the lookout for new ways to improve its Products and Services. For this reason feedback, comments, suggestions or criticisms, however small, are always welcome.

Our policy at SMH Technologies is to comply with all applicable worldwide safety and EMC/EMI regulations. Our products are certified to comply with the European New Approach Directives and the CE mark is applied on all our products.

This product as shipped from the factory has been verified to meet with requirements FCC as a CLASS A product.

In a domestic environment, this product may cause radio interference in which case the user may be required to take adequate prevention measures.

Attaching additional wiring to this product or modifying the product operation from the factory default as shipped may effect its performance and cause interference with other apparatus in the immediate vicinity. If such interference is detected, suitable mitigating measures should be taken.

#### **SMH Technologies**

E-mail (general information): info@smh-tech.com

E-mail (technical support): support@smh-tech.com

Web: http://www.smh-tech.com

#### Important

SMH Technologies reserves the right to make improvements to FlashRunner, its documentation and software routines, without notice. Information in this manual is intended to be accurate and reliable. However, SMH Technologies assumes no responsibility for its use; nor for any infringements of rights of third parties which may result from its use.

SMH TECHNOLOGIES WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF.

#### **Trademarks**

SMH Technologies, SMH Technologies Logo are trademarks of SMH Technologies.

All other product or service names are the property of their respective owners.

# **Contents**

| 1 | BEF   | ORE STARTING                                 | 5  |

|---|-------|----------------------------------------------|----|

|   | 1.1   | IMPORTANT NOTICE TO USERS                    | 5  |

|   | 1.2   | SAFETY                                       |    |

|   | 1.3   | GETTING TECHNICAL SUPPORT                    |    |

|   | 1.4   | Additional Documentation                     |    |

| 2 | OVE   | RVIEW                                        | 8  |

|   | 2.1   | WHAT IS FLASHRUNNER LAN 2.0 NEXT GENERATION? | 8  |

|   | 2.1.1 |                                              |    |

|   | 2.1.2 |                                              |    |

|   | 2.1.3 |                                              |    |

|   | 2.2   | PACKAGE CHECKLIST                            |    |

|   | 2.3   | HARDWARE OVERVIEW                            | 13 |

|   | 2.3.1 |                                              |    |

|   | 2.3.2 | 117                                          |    |

|   | 2.3.3 | 3 LAN Connector                              | 14 |

|   | 2.3.4 | 4 USB Connector                              | 14 |

|   | 2.3.5 | 5 ISP Connectors                             | 14 |

|   | 2.3.6 | 6 LEDs                                       | 15 |

|   | 2.4   | PROGRAMMING DRIVERS AND LICENSES             | 16 |

|   | 2.4.1 | 1 Installing New Licenses                    | 16 |

|   | 2.5   | CHANNEL UPGRADE LICENSES                     | 17 |

|   | 2.6   | Upgrading the Firmware                       | 17 |

| 3 | SYST  | TEM SETUP                                    | 18 |

|   | 3.1   | OVERVIEW                                     | 18 |

|   | 3.2   | SOFTWARE SETUP                               | 18 |

|   | 3.3   | HARDWARE SETUP                               | 18 |

|   | 3.3.1 |                                              |    |

|   | 3.3.2 | Connecting to the Host PC System             | 19 |

|   | 3.3.3 | - · · · · · · · · · · · · · · · · · · ·      |    |

|   | 3.3.4 | 4 Setting Up LAN Settings                    | 19 |

| 4 | CON   | INECTORS                                     | 20 |

| _                                                    | 1.1                                                                          | Overview                                                                                                                                     | ∠∪                   |

|------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                                      | 1.2                                                                          | ISP CONNECTORS                                                                                                                               | 20                   |

| 4                                                    | 1.3                                                                          | ATE CONTROL CONNECTOR                                                                                                                        | 25                   |

| 4                                                    | 1.4                                                                          | USB CONNECTOR                                                                                                                                | 26                   |

| 5                                                    | FLA                                                                          | SHRUNNER LAN 2.0 NEXT GENERATION TOOLS                                                                                                       | 27                   |

| ŗ                                                    | 5.1                                                                          | RELAY BARRIER                                                                                                                                | 27                   |

| į                                                    | 5.2                                                                          | CABLE INTERFACE                                                                                                                              | 32                   |

| 6                                                    | TEC                                                                          | HNICAL SPECIFICATIONS                                                                                                                        | 36                   |

| 6                                                    | 5.1                                                                          | ABSOLUTE MAXIMUM RATINGS                                                                                                                     | 36                   |

| 6                                                    | 5.2                                                                          | DC CHARACTERISTICS AND FUNCTIONAL OPERATING RANGE                                                                                            |                      |

| 6                                                    | 5.3                                                                          | C CHARACTERISTICS (TBW)                                                                                                                      |                      |

|                                                      | 5.4                                                                          | PHYSICAL AND ENVIRONMENTAL SPECIFICATIONS                                                                                                    |                      |

| Ir                                                   | ٦d                                                                           | ex of Figures                                                                                                                                |                      |

|                                                      |                                                                              |                                                                                                                                              | 9                    |

| Fig                                                  | jure 1                                                                       | : FlashRunner LAN 2.0 Next Generation in closed case version                                                                                 |                      |

| Fig<br>Fig                                           | jure 1<br>jure 2                                                             | : FlashRunner LAN 2.0 Next Generation in closed case version<br>2: Power jack, ATE control connector, USB and LAN                            | 13                   |

| Fig<br>Fig                                           | jure 1<br>jure 2<br>jure 3                                                   | : FlashRunner LAN 2.0 Next Generation in closed case version                                                                                 | 13<br>14             |

| Fig<br>Fig<br>Fig                                    | jure 1<br>jure 2<br>jure 3<br>jure 4                                         | 2: FlashRunner LAN 2.0 Next Generation in closed case version<br>2: Power jack, ATE control connector, USB and LAN                           | 13<br>14<br>15       |

| Fig<br>Fig<br>Fig<br>Fig<br>Fig                      | jure 1<br>jure 2<br>jure 3<br>jure 5<br>jure 6                               | E: FlashRunner LAN 2.0 Next Generation in closed case version  B: Power jack, ATE control connector, USB and LAN                             | 13<br>14<br>15<br>21 |

| Fig<br>Fig<br>Fig<br>Fig<br>Fig                      | jure 1<br>jure 2<br>jure 3<br>jure 4<br>jure 5<br>jure 7                     | 1: FlashRunner LAN 2.0 Next Generation in closed case version 2: Power jack, ATE control connector, USB and LAN                              | 1314152122           |

| Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig               | jure 1<br>jure 2<br>jure 3<br>jure 5<br>jure 7<br>jure 8                     | 1: FlashRunner LAN 2.0 Next Generation in closed case version 2: Power jack, ATE control connector, USB and LAN                              |                      |

| Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig        | jure 1<br>jure 2<br>jure 5<br>jure 5<br>jure 6<br>jure 8                     | 1: FlashRunner LAN 2.0 Next Generation in closed case version 2: Power jack, ATE control connector, USB and LAN                              |                      |

| Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig        | jure 1<br>jure 2<br>jure 3<br>jure 5<br>jure 5<br>jure 8<br>jure 9           | I: FlashRunner LAN 2.0 Next Generation in closed case version I: Power jack, ATE control connector, USB and LAN I: ISP" DIN connectors group |                      |

| Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig | jure 1<br>jure 2<br>jure 3<br>jure 5<br>jure 5<br>jure 5<br>jure 9<br>jure 1 | E: FlashRunner LAN 2.0 Next Generation in closed case version                                                                                |                      |

| Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig | jure 1<br>jure 2<br>jure 3<br>jure 5<br>jure 5<br>jure 5<br>jure 1<br>jure 1 | E: FlashRunner LAN 2.0 Next Generation in closed case version                                                                                |                      |

| Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig | jure 1 jure 2 jure 3 jure 5 jure 5 jure 5 jure 1 jure 1 jure 1               | I: FlashRunner LAN 2.0 Next Generation in closed case version                                                                                |                      |

| Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig | jure 1 jure 2 jure 5 jure 5 jure 5 jure 6 jure 1 jure 1 jure 1 jure 1        | E: FlashRunner LAN 2.0 Next Generation in closed case version                                                                                |                      |

# 1 Before Starting

**Note:** Updated version of FlashRunner System Software is available on SMH Technologies website (www.smh-tech.com). Please check it out before continuing to read this documentation.

#### 1.1 Important Notice to Users

While every effort has been made to ensure the accuracy of all information in this document, SMH Technologies assumes no liability to any party for any loss or damage caused by errors or omissions or by statements of any kind in this document, its updates, supplements, or special editions, whether such errors are omissions or statements resulting from negligence, accidents, or any other cause.

## 1.2 Safety

**Note:** Keep FlashRunner LAN 2.0 Next Generation always in a well-ventilated area in order to prevent product overheating, which could affect product performance and, if maintained for a long time, it could damage product hardware components.

FlashRunner LAN 2.0 Next Generation is a low-voltage device. However, when integrating it inside an automatic test equipment or when interfacing it with other systems, take all precautions in order to avoid electrical shocks due to, for example, different ground references.

Make all connections to the target system before applying power to the instrument.

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

To protect FlashRunner LAN 2.0 Next Generation against electrostatic discharge (ESD), always connect yourself to the ground (e.g. via wrist straps) when handling the instrument.

Always store FlashRunner LAN 2.0 Next Generation inside an antistatic bag when not in use.

**Disclaimer:** when integrating FlashRunner LAN 2.0 Next Generation please pay attention to place it in a well-ventilated area in order to avoid overheating related damages.

FlashRunner LAN 2.0 Next Generation has been designed to reach 90 °C (194 °F) in normal operating conditions over its ends.

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

## 1.3 Getting Technical Support

SMH Technologies is continuously working to improve FlashRunner LAN 2.0 Next Generation firmware and to release programming algorithms for new devices. SMH Technologies offers fast and knowledgeable technical support to all of its customers and is always available to solve specific problems or meet specific needs.

To get in touch with SMH Technologies, please refer to the contact information below.

Phone: +39 0434 421111

Fax: +39 0434 639021

Technical Support: support@smh-tech.com

#### 1.4 Additional Documentation

This user's manual provides information about how to setup FlashRunner LAN 2.0 Next Generation and its hardware characteristics.

For information about FlashRunner LAN 2.0 Next Generation commands and their syntax, please refer to the FlashRunner 2.0 Programmer's Manual, included (in PDF format) in FlashRunner 2.0 setup.

## 2 Overview

#### 2.1 What is FlashRunner LAN 2.0 Next Generation?

FlashRunner LAN 2.0 Next Generation is a compact high-integration in-system gang programmer, based on the new and innovative FlashRunner 2.0 cutting-edge technology. FlashRunner LAN 2.0 Next Generation is designed for programming multi-PCB panel assemblies, with microcontroller, eMMC and NAND memories. This means:

- Extremely fast programming (the fastest in-system programming system on the market);

- Standalone operations for easy ATE integration

- Brand new Graphical User Interface focused on Setup, Production and Security features

- Compact and robust design for production environments.

SYNERGY OF IN-SYSTEM PROGRAMMING LEADER

FlashRunner LAN 2.0 Next Generation is composed of a carrier board that hosts up to 4 programming channels.

The engine board on top of it is a System on Module enclosing FlashRunner 2.0 core technology in a compact and easy to integrate format.

FlashRunner LAN 2.0 Next Generation is available in different enclosures:

- FRLAN2P0NXG-OF

- FRLAN2P0NXG-CS

open frame version closed case version

Figure 1: FlashRunner LAN 2.0 Next Generation in closed case version

FlashRunner LAN 2.0 Next Generation comes in one hardware solution, enabling 1 channel for device programming.

Products upgrade for up to 4 active channels are available by asking your sales reference for a specific upgrade license.

In all of the above configurations, each ISP channel is composed of:

- Eight digital, bidirectional lines;

- Two power lines;

- Ten ground lines (one per digital signal and power line)

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

#### 2.1.1 General features

- Fastest programming algorithms (as fast as target device's memory technology limit), approved by silicon manufacturers;

- Up to 4 parallel and independent channels

- Easy ATE integration;

- Standalone operations

- Controllable by ATE through optoisolated LAN and USB, or parallel control lines;

- Supports most ISP protocols (BDM, JTAG, SPI, I2C, MON, ICC, SCI, UART, etc.);

- Flexible, fully configurable;

- Compact and robust design for production environments:

- 10Mbyte/sec host data transfer.

#### 2.1.2 Hardware features

- ISP lines:

- 8 digital I/O lines; 1 ground line per signal;

- 2 programmable output voltages; 1 ground line per power line;

- 1 GBytes on-board RAM memory;

- On-board timekeeper and calendar for time-stamped log file;

- LAN Communication Interface

- Optoisolated USB communication interface.

- Optoisolated ATE interface for standalone operations

- Programming voltage measure of each channel

- Programming current measure of each channel

#### 2.1.3 Software features

- Linux based operating system;

- FlashRunner 2.0 WorkBench: the new user-friendly Graphical User Interface (Windows, Linux and Mac compatible)

- Controllable by any host system through a terminal utility and simple ASCII protocol;

- Up to 32 hardware-selectable projects in Standalone Mode, unlimited software-selectable projects in Host Mode;

YNFRGY OF IN-SYSTEM PROGRAMMING I FADERS

- Interface Library DLL to control the instrument from within user-written applications;

- Optional customer binary file cryptography to ensure antipiracy protection

- Log file and production report file;

- Erase, blank check, program, read, verify, oscillator trimming, etc.

## 2.2 Package Checklist

FlashRunner LAN 2.0 Next Generation comes in packaging variants: Open-Frame and Closed-Case.

The relative packages include the following items:

Table 1: FlashRunner 2.0 NXG Open Frame Package Checklist

| Qty. | Description                                         |  |

|------|-----------------------------------------------------|--|

| 1    | FlashRunner LAN 2.0 Next Generation Open Frame Unit |  |

| 1    | ISP Flat Cable Extension 30cm                       |  |

| 1    | Ethernet cross cable 2 meter RJ45                   |  |

| 1    | Micro USB2 cable 1.8 meter                          |  |

| 1    | Control Interface Flat Cable 15cm                   |  |

| 1    | Control Interface Board                             |  |

| 1    | Cable Interface Board                               |  |

| 1    | DIN41612 Connector 48 pin male IDC                  |  |

| 2    | Cable Interface Strip connector 10 x 2 h=8mm        |  |

| 1    | Control Interface Strip connector 7 x 2 h=8mm       |  |

| 1    | 3-Year Warranty Sheet                               |  |

| 1    | FRLAN2P0NXG Pinout Reference                        |  |

| 1    | FRLAN2P0NXG Quick Start Guide                       |  |

| 1    | FRLAN2P0NXG Connection Reference Document           |  |

| 1    | 15V 40W AC/DC Wall Switching Power Adapter          |  |

| 2    | M3x6 round head allen key screws                    |  |

Table 2: FlashRunner 2.0 NXG Closed Case Package Checklist

| Qty. | Description                                          |  |

|------|------------------------------------------------------|--|

| 1    | FlashRunner LAN 2.0 Next Generation Closed Case Unit |  |

| 1    | Control Interface Flat Cable 15cm                    |  |

| 1    | ISP Flat Cable Extension 30cm                        |  |

| 1    | Ethernet cross cable 2 meter RJ45                    |  |

| 1    | Micro USB2 cable 1.8 meter                           |  |

| 1    | Panel Bracket for FRLAN2P0NXG-CS                     |  |

| 1    | Control Interface Board                              |  |

| 1    | Cable Interface Board                                |  |

| 1    | DIN41612 Connector 48 pin male IDC                   |  |

| 2    | Cable Interface Strip connector 10 x 2 h=8mm         |  |

| 1    | Control Interface Strip connector 7 x 2 h=8mm        |  |

| 1    | 3-Year Warranty Sheet                                |  |

| 1    | FRLAN2P0NXG Quick Start Guide                        |  |

| 1    | FRLAN2P0NXG Pinout Reference                         |  |

| 1    | 15V 40W AC/DC Wall Switching Power Adapter           |  |

| 1    | FRLAN2P0NXG Connection Reference Document            |  |

| 2    | M3x6 round head hex key screws                       |  |

| 2    | M3x6 TCEI hex socket screws                          |  |

When either a 3 or 4 channels version is purchased, the following items will be included in the package:

Table 3: Package addons for 3/4 channels versions

|      | rable of rabinage addens for of rahamiles versions |  |  |

|------|----------------------------------------------------|--|--|

| Qty. | Description                                        |  |  |

| 1    | Cable Interface Board                              |  |  |

| 1    | ISP Flat Cable Extension 30cm                      |  |  |

| 1    | DIN41612 Connector 48 pin male IDC                 |  |  |

| 2    | Cable Interface Strip connector 10 x 2 h=8mm       |  |  |

#### 2.3 Hardware Overview

#### 2.3.1 Power Supply

FlashRunner LAN 2.0 Next Generation is powered through a 15V power supply connected to a DC plug connector.

#### 2.3.2 ATE Control Connector

ATE Control DIN Connectors are used by an ATE system to control FlashRunner LAN 2.0 Next Generation instead of communicating with the instrument through the USB or LAN port. You could define and start a project, and check results. For more information please check chapter 4.3.

Figure 2: Power jack, ATE control connector, USB and LAN

#### 2.3.3 LAN Connector

LAN Connector is used to communicate with Host PC system. Use provided cross cable to connect FlashRunner LAN 2.0 Next Generation with your PC. For more information check chapter 2.3.3 and check related documentation on FlashRunner 2.0 Programmer's Manual to correctly set up your host PC system

#### 2.3.4 **USB Connector**

Alternatively, communication with the host PC can be done with the micro USB connector. Use the provided USB cable to connect FlashRunner LAN 2.0 Next Generation with your PC. For more information check chapter 2.3.4 and check related documentation on FlashRunner 2.0 Programmer's Manual to correctly set up your host PC system

#### 2.3.5 **ISP Connectors**

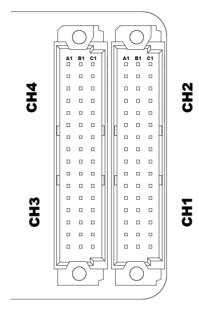

In Illustration 3 you can see two ISP connectors, the one on the right will define channels 1 and 2, the left one will define channels 3 and 4. For more information check chapter 2.3.5.

Figure 3: "ISP" DIN connectors group

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

#### 2.3.6 **LEDs**

- POWER: the instrument is turned on

- STATUS: indicates system warnings

- BUSY: turned on when a project is running

- CHANNEL 1..4: programming result.

Green: programming successful, Red: programming failed

The STATUS LED indicates whether the Hardware SelfTest, running during the boot phase that tests all the hardware peripherals connected on the i2c buses, such as DAC and ADC for the measurement of VPROG currents and voltages has been successful. If the test passes, the STATUS\_LED stays on. If the test fails, the STATUS LED blinks. If the STATUS LED remains off there is something wrong.

Figure 4: FlashRunner LAN 2.0 Next Generation Top Panel

#### 2.4 Programming Drivers and Licenses

FlashRunner LAN 2.0 Next Generation includes programming drivers for several devices. To program a specific device, however, a specific license file for that device, that family or that silicon producer must be purchased.

**Note:** FlashRunner LAN 2.0 Next Generation comes already preinstalled with the license(s) you specified at the moment of purchase. You can purchase additional licenses at any future moment.

Programming drivers and license files are stored inside FlashRunner LAN 2.0 Next Generation storage memory (see the FlashRunner 2.0 Programmer's Manual for more information).

There are several types of licensing:

- Single device license: only that single device programming is enabled

- Family license: only a single device family programming is enabled

- Silicon Producer license: only a single device silicon producer is enabled

#### 2.4.1 Installing New Licenses

When you buy an additional license for a specific device, you will get a license file (.lic);

If you ordered a new device development, you will also receive:

A driver file (.so)

For detailed information on how to update FlashRunner LAN 2.0 Next Generation please check FlashRunner 2.0 Programmer's Manual.

SYNERGY OF IN-SYSTEM PROGRAMMING LEADER

### 2.5 Channel Upgrade Licenses

If you would like to upgrade from FR2.0A4 to FR2.0A8, or from FR2.0A12 to FR2.0A16, you could purchase a Channel Upgrade License. Please ask our Sales Team (sales@smh-tech.com).

## 2.6 Upgrading the Firmware

FlashRunner LAN 2.0 Next Generation firmware can be easily upgraded using the FlashRunner 2.0 WorkBench software. For more information, please refer to the FlashRunner 2.0 Programmer's Manual.

# 3 System Setup

#### 3.1 Overview

**Note:** Keep FlashRunner LAN 2.0 Next Generation always in a well-ventilated area in order to prevent product overheating, which could affect product performance and, if maintained for a long time, it could damage product hardware components.

This chapter will explain how to set up FlashRunner LAN 2.0 Next Generation for the first time. The new FR2.0 WorkBench project Wizard allows an easy and fast system setup.

When moving FlashRunner LAN 2.0 Next Generation to the production environment, you can take full advantage of the FR2.0 WorkBench GUI Production Tool (Host mode) or let the instrument be controlled through the "ATE Control" interface (Standalone mode).

For more information about Standalone mode and Host mode, see the FlashRunner 2.0 Programmer's Manual.

## 3.2 Software Setup

Please refer to the "System Setup/Upgrade" chapter of FlashRunner 2.0 Programmer's Manual.

#### 3.3 Hardware Setup

To set up FlashRunner LAN 2.0 Next Generation, you must follow the steps below in the following order:

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

- Interface FlashRunner LAN 2.0 Next Generation with your test/programming equipment;

- Connect FlashRunner LAN 2.0 Next Generation to host PC system (if you use it in Host Mode);

- Power up FlashRunner LAN 2.0 Next Generation;

- Set up LAN settings (if you use the Ethernet connection);

#### 3.3.1 Interfacing with your Test/Programming equipment

Build one or more ISP cables to connect FlashRunner LAN 2.0 Next Generation ISP connectors to your target board(s). Wire up all the required connections (power, oscillator, ISP signals) to target microcontrollers using the PinMap tool (for more details please check the related chapter on FlashRunner 2.0 Programmer's Manual).

#### 3.3.2 Connecting to the Host PC System

You can connect FlashRunner LAN 2.0 Next Generation to the host system through either the USB or LAN port.

FlashRunner LAN 2.0 Next Generation comes with a USB cable and an Ethernet cross cable to connect directly to a host PC.

#### 3.3.3 Powering Up

Power up FlashRunner LAN 2.0 Next Generation by connecting the included power supply to DC plug connector.

#### 3.3.4 Setting Up LAN Settings

If you connected FlashRunner LAN 2.0 Next Generation to the host PC using the Ethernet connection, you need to set up the FlashRunner LAN 2.0 Next Generation IP address. To learn how to set up the FlashRunner LAN 2.0 Next Generation address, please refer to the FlashRunner 2.0 Programmer's Manual.

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

## 4 Connectors

#### 4.1 Overview

FlashRunner LAN 2.0 Next Generation connects to your programming/testing system through:

- "ISP" connectors: 48 way, 3 rows, DIN 41612, pitch = 2.54mm (male)

- "ATE CONTROL" connector: 14 way, 2 rows, pitch = 1.27mm (male)

- Additionally, a micro USB and Ethernet connectors are provided to interface fully with the ATE system.

#### 4.2 ISP Connectors

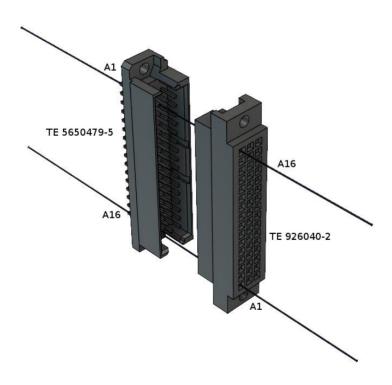

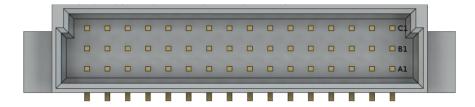

"ISP" connectors group signals needed to program up to 4 target devices. These connectors are type R/2 DIN41612 (TE part number 5650479-5) with several input/output lines and power lines.

**Note:** *ISP* and *I/O* signals are not optoisolated and are referenced to GND (power supply ground).

Additionally, in order to avoid undesired current loops between FlashRunner LAN NXG power supply and target board, a power supply with a floating output (ground not referenced to the earth potential) should be used.

**Note on DIN41612 connectors:** The use of these connectors implies that the pin assignment of a possible type C/2 female connector will be mirrored over the rows with respect to the pin assignment of the R/2 male onboard. Therefore, pin A1 of the R/2 male will correspond to A16 on the C/2 female, B1 will correspond to B16 and so forth. Please compare with given illustration.

Figure 5: DIN41612 mating pin assignment example

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

Società Unipersonale

Figure 6: ISP Connector

Table 4: ISP Connector Signals (Channels 1 and 2)

|       |                | Connector Signals (Charmers 1 and 2)         |

|-------|----------------|----------------------------------------------|

| Pin # | Signal Name    | Description                                  |

| A1    | VPROG0_CH2     | ISP Channel 2: Programmable voltage 0        |

| A2    | VPROG1_GND_CH2 | ISP Channel 2: Programmable voltage 1 Ground |

| A3    | DIO1_CH2       | ISP Channel 2: Digital input/output 1        |

| A4    | DIO2_GND_CH2   | ISP Channel 2: Digital input/output 2 Ground |

| A5    | DIO4_CH2       | ISP Channel 2: Digital input/output 4        |

| A6    | DIO5_GND_CH2   | ISP Channel 2: Digital input/output 5 Ground |

| A7    | DIO7_CH2       | ISP Channel 2: Digital input/output 7        |

| A8    | PWR_RLY_CH2    | ISP Channel 2: Relay Barrier Power Source    |

| A9    | PWR_RLY_CH1    | ISP Channel 1: Relay Barrier Power Source    |

| A10   | VPROG0_CH1     | ISP Channel 1: Programmable voltage 0        |

| A11   | VPROG1_GND_CH1 | ISP Channel 1: Programmable voltage 1 Ground |

| A12   | DIO1_CH1       | ISP Channel 1: Digital input/output 1        |

| A13   | DIO2_GND_CH1   | ISP Channel 1: Digital input/output 2 Ground |

| A14   | DIO4_CH1       | ISP Channel 1: Digital input/output 4        |

| A15   | DIO5_GND_CH1   | ISP Channel 1: Digital input/output 5 Ground |

| A16   | DIO7_CH1       | ISP Channel 1: Digital input/output 7        |

| В1    | VPROG0_GND_CH2 | ISP Channel 2: Programmable voltage 0 Ground |

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

| Pin# | Signal Name    | Description                                  |

|------|----------------|----------------------------------------------|

| В2   | DIO0_CH2       | ISP Channel 2: Digital input/output 0        |

| В3   | DIO1_GND_CH2   | ISP Channel 2: Digital input/output 1 Ground |

| В4   | DIO3_CH2       | ISP Channel 2: Digital input/output 3        |

| В5   | DIO4_GND_CH2   | ISP Channel 2: Digital input/output 4 Ground |

| В6   | DIO6_CH2       | ISP Channel 2: Digital input/output 6        |

| В7   | DIO7_GND_CH2   | ISP Channel 2: Digital input/output 7 Ground |

| В8   | RLY_ON_CH2     | ISP Channel 2: Relay Barrier Driver Output   |

| В9   | RLY_ON_CH1     | ISP Channel 1: Relay Barrier Driver Output   |

| B10  | VPROG0_GND_CH1 | ISP Channel 1: Programmable voltage 0 Ground |

| B11  | DIO0_CH1       | ISP Channel 1: Digital input/output 0        |

| B12  | DIO1_GND_CH1   | ISP Channel 1: Digital input/output 1 Ground |

| В13  | DIO3_CH1       | ISP Channel 1: Digital input/output 3        |

| В14  | DIO4_GND_CH1   | ISP Channel 1: Digital input/output 4 Ground |

| B15  | DIO6_CH1       | ISP Channel 1: Digital input/output 6        |

| B16  | DIO7_GND_CH1   | ISP Channel 1: Digital input/output 7 Ground |

| C1   | VPROG1_CH2     | ISP Channel 2: Programmable voltage 1        |

| C2   | DIO0_GND_CH2   | ISP Channel 2: Digital input/output 0 Ground |

| C3   | DIO2_CH2       | ISP Channel 2: Digital input/output 2        |

| C4   | DIO3_GND_CH2   | ISP Channel 2: Digital input/output 3 Ground |

| C5   | DIO5_CH2       | ISP Channel 2: Digital input/output 5        |

| C6   | DIO6_GND_CH2   | ISP Channel 2: Digital input/output 6 Ground |

| C7   | RESERVED_CH2   | ISP Channel 2: Reserved Pin                  |

| C8   | GND_RLY_CH2    | ISP Channel 2: Relay Barrier Ground          |

| C9   | GND_RLY_CH1    | ISP Channel 1: Relay Barrier Ground          |

| C10  | VPROG1_CH1     | ISP Channel 1: Programmable voltage 1        |

| C11  | DIO0_GND_CH1   | ISP Channel 1: Digital input/output 0 Ground |

| C12  | DIO2_CH1       | ISP Channel 1: Digital input/output 2        |

| C13  | DIO3_GND_CH1   | ISP Channel 1: Digital input/output 3 Ground |

| C14  | DIO5_CH1       | ISP Channel 1: Digital input/output 5        |

| C15  | DIO6_GND_CH1   | ISP Channel 1: Digital input/output 6 Ground |

| C16  | RESERVED_CH1   | ISP Channel 1: Reserved Pin                  |

Table 5: ISP Connector Signals (Channels 3 and 4)

| Pin# | Signal Name    | Description                                  |

|------|----------------|----------------------------------------------|

| A1   | VPROG0_CH4     | ISP Channel 4: Programmable voltage 0        |

| A2   | VPROG1_GND_CH4 | ISP Channel 4: Programmable voltage 1 Ground |

| A3   | DIO1_CH4       | ISP Channel 4: Digital input/output 1        |

| A4   | DIO2_GND_CH4   | ISP Channel 4: Digital input/output 2 Ground |

| A5   | DIO4_CH4       | ISP Channel 4: Digital input/output 4        |

| A6   | DIO5_GND_CH4   | ISP Channel 4: Digital input/output 5 Ground |

| A7   | DIO7_CH4       | ISP Channel 4: Digital input/output 7        |

| A8   | PWR_RLY_CH4    | ISP Channel 4: Relay Barrier Power Source    |

SYNERGY OF IN-SYSTEM PROGRAMMING LEADER

| Pin# | Signal Name    | Description                                  |

|------|----------------|----------------------------------------------|

| A9   | PWR_RLY_CH3    | ISP Channel 3: Relay Barrier Power Source    |

| A10  | VPROG0_CH3     | ISP Channel 3: Programmable voltage 0        |

| A11  | VPROG1_GND_CH3 | ISP Channel 3: Programmable voltage 1 Ground |

| A12  | DIO1_CH3       | ISP Channel 3: Digital input/output 1        |

| A13  | DIO2_GND_CH3   | ISP Channel 3: Digital input/output 2 Ground |

| A14  | DIO4_CH3       | ISP Channel 3: Digital input/output 4        |

| A15  | DIO5_GND_CH3   | ISP Channel 3: Digital input/output 5 Ground |

| A16  | DIO7_CH3       | ISP Channel 3: Digital input/output 7        |

| В1   | VPROG0_GND_CH4 | ISP Channel 4: Programmable voltage 0 Ground |

| В2   | DIO0_CH4       | ISP Channel 4: Digital input/output 0        |

| В3   | DIO1_GND_CH4   | ISP Channel 4: Digital input/output 1 Ground |

| В4   | DIO3_CH4       | ISP Channel 4: Digital input/output 3        |

| В5   | DIO4_GND_CH4   | ISP Channel 4: Digital input/output 4 Ground |

| В6   | DIO6_CH4       | ISP Channel 4: Digital input/output 6        |

| В7   | DIO7_GND_CH4   | ISP Channel 4: Digital input/output 7 Ground |

| В8   | RLY_ON_CH4     | ISP Channel 4: Relay Barrier Driver Output   |

| В9   | RLY_ON_CH3     | ISP Channel 3: Relay Barrier Driver Output   |

| B10  | VPROG0_GND_CH3 | ISP Channel 3: Programmable voltage 0 Ground |

| B11  | DIO0_CH3       | ISP Channel 3: Digital input/output 0        |

| B12  | DIO1_GND_CH3   | ISP Channel 3: Digital input/output 1 Ground |

| B13  | DIO3_CH3       | ISP Channel 3: Digital input/output 3        |

| B14  | DIO4_GND_CH3   | ISP Channel 3: Digital input/output 4 Ground |

| B15  | DIO6_CH3       | ISP Channel 3: Digital input/output 6        |

| B16  | DIO7_GND_CH3   | ISP Channel 3: Digital input/output 7 Ground |

| C1   | VPROG1_CH4     | ISP Channel 4: Programmable voltage 1        |

| C2   | DIO0_GND_CH4   | ISP Channel 4: Digital input/output 0 Ground |

| C3   | DIO2_CH4       | ISP Channel 4: Digital input/output 2        |

| C4   | DIO3_GND_CH4   | ISP Channel 4: Digital input/output 3 Ground |

| C5   | DIO5_CH4       | ISP Channel 4: Digital input/output 5        |

| C6   | DIO6_GND_CH4   | ISP Channel 4: Digital input/output 6 Ground |

| C7   | RESERVED_CH4   | ISP Channel 4: reserved Pin                  |

| C8   | GND_RLY_CH4    | ISP Channel 4: Relay Barrier Ground          |

| C9   | GND_RLY_CH3    | ISP Channel 3: Relay Barrier Ground          |

| C10  | VPROG1_CH3     | ISP Channel 3: Programmable voltage 1        |

| C11  | DIO0_GND_CH3   | ISP Channel 3: Digital input/output 0 Ground |

| C12  | DIO2_CH3       | ISP Channel 3: Digital input/output 2        |

| C13  | DIO3_GND_CH3   | ISP Channel 3: Digital input/output 3 Ground |

| C14  | DIO5_CH3       | ISP Channel 3: Digital input/output 5        |

| C15  | DIO6_GND_CH3   | ISP Channel 3: Digital input/output 6 Ground |

| C16  | RESERVED_CH3   | ISP Channel 3: Reserved Pin                  |

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

24

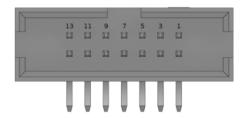

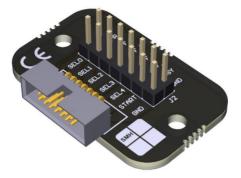

## 4.3 ATE Control Connector

ATE Control Connector is used to communicate with the host system and for integration with automatic programming/testing equipment (ATE).

**Note:** all control signals are referenced to GND\_I, separate from GND. This allows a host system to safely communicate with FlashRunner LAN 2.0 Next Generation even when the target boards have different ground reference compared to the host system's (and it's not possible to connect them together).

Figure 7: ATE CONTROL Connector

Table 6: Control Connector Signals

| Pin# | Signal Name   | Description                                                     |

|------|---------------|-----------------------------------------------------------------|

| 1    | SEL0          | Project selection 0 (input, referenced to GND_I)                |

| 2    | 5V_I_FUSE     | 5V output (output, fuse-protected, referenced to GND_I)         |

| 3    | SEL1          | Project selection 1 (input, referenced to GND_I)                |

| 4    | PASS/FAIL_CH1 | Programming channel 1 PASS/FAIL (output, referenced to GND_I)   |

| 5    | SEL2          | Project selection 2 (input, referenced to GND_I)                |

| 6    | PASS/FAIL_CH2 | Programming channel 2 PASS/FAIL (output, referenced to GND_I)   |

| 7    | SEL3          | Project selection 3 (input, referenced to GND_I)                |

| 8    | PASS/FAIL_CH3 | Programming channel 3 PASS/FAIL (output, referenced to GND_I)   |

| 9    | SEL4          | Project selection 4 (input, referenced to GND_I)                |

| 10   | PASS/FAIL_CH4 | Programming channel 4 PASS/FAIL (output, referenced to GND_I)   |

| 11   | START         | Selected Project START (input, referenced to GND_I, active low) |

| 12   | BUSY          | Selected Project BUSY (output, referenced to GND_I, active low) |

| 13   | GND_I         | Ground                                                          |

| 14   | GND_I         | Ground                                                          |

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

You can use the provided expansion board to connect to the control interface's signals which are indicated on the board's silkscreen.

Figure 8: Control Interface expansion board

#### 4.4 USB Connector

The USB-B connector can be used to communicate with the ATE system.

Note: USB signals are referenced to GND\_USB, separate from GND, and GND\_I.

# 5 FlashRunner LAN 2.0 Next Generation Tools

## 5.1 Relay Barrier

Relay barrier is functional to provide galvanic isolation between FlashRunner and the UUTs. It is available in a two-channel version:

- FRLAN2P0NXGRB (Relay Barrier for FRLAN2P0NXG)

It can be upgraded to a 4 channels version according to your needs. Please contact your sales representative for further information.

Figure 9: FRLAN2P0NXGRB two channels relay barrier

Relay barrier is self-powered when plugged into FlashRunner LAN 2.0 Next Generation.

YNERGY OF IN-SYSTEM PROGRAMMING I FADERS

The driving signals for the relays are given by the FlashRunner through the dedicated pins.

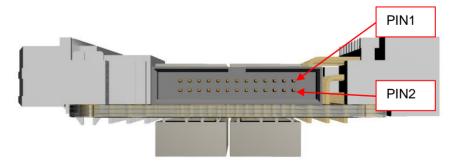

Figure 10: Relay Barrier ISP connector front view

Table 7: Relay Barrier ISP "output" signals

|       | _              | 7: Relay Barrier ISP "output" signals        |

|-------|----------------|----------------------------------------------|

| Pin # | Signal Name    | Description                                  |

| A1    | DIO7_CHA       | ISP Channel A: Digital input/output 7        |

| A2    | DIO5_GND_CHA   | ISP Channel A: Digital input/output 5 Ground |

| А3    | DIO4_CHA       | ISP Channel A: Digital input/output 4        |

| A4    | DIO2_GND_CHA   | ISP Channel A: Digital input/output 2 Ground |

| A5    | DIO1_CHA       | ISP Channel A: Digital input/output 1        |

| A6    | VPROG1_GND_CHA | ISP Channel A: Programmable voltage 1 Ground |

| A7    | VPROG0_CHA     | ISP Channel A: Programmable voltage 0        |

| A8    | NC             | Not Connected                                |

| A9    | NC             | Not Connected                                |

| A10   | DIO7_CHB       | ISP Channel B: Digital input/output 7        |

| A11   | DIO5_GND_CHB   | ISP Channel B: Digital input/output 5 Ground |

| A12   | DIO4_CHB       | ISP Channel B: Digital input/output 4        |

| A13   | DIO2_GND_CHB   | ISP Channel B: Digital input/output 2 Ground |

| A14   | DIO1_CHB       | ISP Channel B: Digital input/output 1        |

| A15   | VPROG1_GND_CHB | ISP Channel B: Programmable voltage 1 Ground |

| A16   | VPROG0_CHB     | ISP Channel B: Programmable voltage 0        |

| B1    | DIO7_GND_CHA   | ISP Channel A: Digital input/output 7 Ground |

| B2    | DIO6_CHA       | ISP Channel A: Digital input/output 6        |

| В3    | DIO4_GND_CHA   | ISP Channel A: Digital input/output 4 Ground |

| B4    | DIO3_CHA       | ISP Channel A: Digital input/output 3        |

| B5    | DIO1_GND_CHA   | ISP Channel A: Digital input/output 1 Ground |

| В6    | DIO0_CHA       | ISP Channel A: Digital input/output 0        |

| В7    | VPROG0_GND_CHA | ISP Channel A: Programmable voltage 0 Ground |

| B8    | NC             | Not Connected                                |

| В9    | NC             | Not Connected                                |

| B10   | DIO7_GND_CHB   | ISP Channel B: Digital input/output 7 Ground |

| B11   | DIO6_CHB       | ISP Channel B: Digital input/output 6        |

|       |                |                                              |

SYNERGY OF IN-SYSTEM PROGRAMMING LEADER

| Pin# | Signal Name    | Description                                  |

|------|----------------|----------------------------------------------|

| B12  | DIO4_GND_CHB   | ISP Channel B: Digital input/output 4 Ground |

| B13  | DIO3_CHB       | ISP Channel B: Digital input/output 3        |

| B14  | DIO1_GND_CHB   | ISP Channel B: Digital input/output 1 Ground |

| B15  | DIO0_CHB       | ISP Channel B: Digital input/output 0        |

| B16  | VPROG0_GND_CHB | ISP Channel B: Programmable voltage 0 Ground |

| C1   | NC             | Not Connected                                |

| C2   | DIO6_GND_CHA   | ISP Channel A: Digital input/output 6 Ground |

| C3   | DIO5_CHA       | ISP Channel A: Digital input/output 5        |

| C4   | DIO3_GND_CHA   | ISP Channel A: Digital input/output 3 Ground |

| C5   | DIO2_CHA       | ISP Channel A: Digital input/output 2        |

| C6   | DIO0_GND_CHA   | ISP Channel A: Digital input/output 0 Ground |

| C7   | VPROG1_CHA     | ISP Channel A: Programmable voltage 1        |

| C8   | GND_RLY_CHA    | ISP Channel A: Relay Barrier Ground          |

| C9   | GND_RLY_CHB    | ISP Channel B: Relay Barrier Ground          |

| C10  | NC             | Not Connected                                |

| C11  | DIO6_GND_CHB   | ISP Channel B: Digital input/output 6 Ground |

| C12  | DIO5_CHB       | ISP Channel B: Digital input/output 5        |

| C13  | DIO3_GND_CHB   | ISP Channel B: Digital input/output 3 Ground |

| C14  | DIO2_CHB       | ISP Channel B: Digital input/output 2        |

| C15  | DIO0_GND_CHB   | ISP Channel B: Digital input/output 0 Ground |

| C16  | VPROG1_CHB     | ISP Channel B: Programmable voltage 1        |

A 26 pins auxiliary input connector is available onboard, which connects to the output pins of the two channels when the relays are open.

You can use the provided Auxiliary Interface board to connect your signals to the UUT when not using the programmer's digital IOs.

Figure 11: FRLAN2P0NXGRB Auxiliary input connector

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

Società Unipersonale

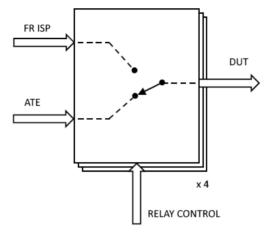

#### Block diagram of the ISP lines switching capabilities:

Figure 12: Relay Barrier Application Note

Table 8: Auxiliary Connector Pinout

| Pin# | Signal Name  | Description                                  |

|------|--------------|----------------------------------------------|

| 1    | AUX_A_DIO0   | ISP Channel A: Digital input/output 0        |

| 2    | AUX_B_VPROG0 | ISP Channel B: Digital input/output Vprog0   |

| 3    | AUX_A_DIO1   | ISP Channel A: Digital input/output 1        |

| 4    | AUX_B_VPROG1 | ISP Channel B: Digital input/output VProg1   |

| 5    | AUX_A_DIO2   | ISP Channel A: Digital input/output 2        |

| 6    | AUX_B_GND0   | ISP Channel B: Digital input/output Ground 0 |

| 7    | AUX_A_DIO3   | ISP Channel A: Digital input/output 3        |

| 8    | AUX_B_GND1   | ISP Channel B: Digital input/output Ground 1 |

| 9    | AUX_A_DIO4   | ISP Channel A: Digital input/output 4        |

| 10   | AUX_B_DIO0   | ISP Channel B: Digital input/output 0        |

| 11   | AUX_A_DIO5   | ISP Channel A: Digital input/output 5        |

| 12   | AUX_B_DIO1   | ISP Channel B: Digital input/output 1        |

| 13   | AUX_A_DIO6   | ISP Channel A: Digital input/output 6        |

| 14   | AUX_B_DIO2   | ISP Channel B: Digital input/output 2        |

| 15   | AUX_A_DIO7   | ISP Channel A: Digital input/output 7        |

| 16   | AUX_B_DIO3   | ISP Channel B: Digital input/output 3        |

| 17   | AUX_A_VPROG0 | ISP Channel A: Digital input/output VProg0   |

| 18   | AUX_B_DIO4   | ISP Channel B: Digital input/output 4        |

| 19   | AUX_A_VPROG1 | ISP Channel A: Digital input/output VProg1   |

| 20   | AUX_B_DIO5   | ISP Channel B: Digital input/output 5        |

SYNERGY OF IN-SYSTEM PROGRAMMING LEADE

| Pin# | Signal Name | Description                                  |

|------|-------------|----------------------------------------------|

| 21   | AUX_A_GND0  | ISP Channel A: Digital input/output Ground 0 |

| 22   | AUX_B_DIO6  | ISP Channel B: Digital input/output 6        |

| 23   | AUX_A_GND1  | ISP Channel A: Digital input/output Ground 1 |

| 24   | AUX_B_DIO7  | ISP Channel B: Digital input/output 7        |

| 25   | AUX_A_GND2  | ISP Channel A: Digital input/output Ground 2 |

| 26   | AUX_B_GND2  | ISP Channel B: Digital input/output Ground 2 |

Figure 13: Auxiliary interface expansion board for relay barrier

| Parameter                                    | Value                                                |

|----------------------------------------------|------------------------------------------------------|

| Supply voltage on line POWER (reference GND) | +15V                                                 |

| FRLAN2P0NXGRB Dimensions                     | 58.6 mm x 60 mm x16 mm                               |

| "ISP" connectors type                        | DIN41612 type C/2 male output, type R/2 female input |

| Auxiliary connector                          | 26 pin box header 1.27mm pitch (0.50 mils)           |

## 5.2 Cable Interface

A cable interface is available for the FlashRunner LAN2P0 NXG to connect the targets using our special twisted cables, keeping good signals integrity.

Each header connector (H1..H4) is the output of one programming channel and can be connected to a FRHDRPSTR through a FRCABLE.

Figure 14: Auxiliary interface expansion board for relay barrier

| Parameter              | Value                                    |

|------------------------|------------------------------------------|

| FR2P0INTF08 Dimensions | 60 x 40 x 19 mm                          |

| FRHDRPSTR Dimensions   | 46 x 30 mm                               |

| "ISP" connectors type  | 48 way, 3 row, DIN 41612, pitch = 2.54mm |

| Header connectors type | 20 way, 2 row, pitch =1,27mm             |

| H3-1                   | H4-1                                     |

| нз                     | PI P |

| H3-2                   | H4-2                                     |

| SMH<br>ct              | Technologies" a ag                       |

| H1-1                   | H2-1                                     |

| O <sub>E</sub>         | H2                                       |

| H1-2                   | H2-2                                     |

SYNERGY OF IN-SYSTEM PROGRAMMING LEADER

Società Unipersonale

info@smh-tech.com

Table 9: Header Connector Signals Channel 1

| Pin#  | Signal Name    | Description                                  |

|-------|----------------|----------------------------------------------|

| H1-1  | DIO0_CH1       | ISP Channel 1: Digital input/output 0        |

| H1-2  | DIO0_GND_CH1   | ISP Channel 1: Digital input/output 0 Ground |

| H1-3  | DIO1_CH1       | ISP Channel 1: Digital input/output 1        |

| H1-4  | DIO1_GND_CH1   | ISP Channel 1: Digital input/output 1 Ground |

| H1-5  | DIO2_CH1       | ISP Channel 1: Digital input/output 2        |

| H1-6  | DIO2_GND_CH1   | ISP Channel 1: Digital input/output 2 Ground |

| H1-7  | DIO3_CH1       | ISP Channel 1: Digital input/output 3        |

| H1-8  | DIO3_GND_CH1   | ISP Channel 1: Digital input/output 3 Ground |

| H1-9  | DIO4_CH1       | ISP Channel 1: Digital input/output 4        |

| H1-10 | DIO4_GND_CH1   | ISP Channel 1: Digital input/output 4 Ground |

| H1-11 | DIO5_CH1       | ISP Channel 1: Digital input/output 5        |

| H1-12 | DIO5_GND_CH1   | ISP Channel 1: Digital input/output 5 Ground |

| H1-13 | DIO6_CH1       | ISP Channel 1: Digital input/output 6        |

| H1-14 | DIO6_GND_CH1   | ISP Channel 1: Digital input/output 6 Ground |

| H1-15 | DIO7_CH1       | ISP Channel 1: Digital input/output 7        |

| H1-16 | DIO7_GND_CH1   | ISP Channel 1: Digital input/output 7 Ground |

| H1-17 | VPROG0_CH1     | ISP Channel 1: Programmable voltage 0        |

| H1-18 | VPROG0_GND_CH1 | ISP Channel 1: Programmable voltage 0 Ground |

| H1-19 | VPROG1_CH1     | ISP Channel 1: Programmable voltage 1        |

| H1-20 | VPROG1_GND_CH1 | ISP Channel 1: Programmable voltage 1 Ground |

Table 10: Header Connector Signals Channel 2

| Pin#  | Signal Name    | Description                                  |

|-------|----------------|----------------------------------------------|

| H2-1  | DIO0_CH2       | ISP Channel 2: Digital input/output 0        |

| H2-2  | DIO0_GND_CH2   | ISP Channel 2: Digital input/output 0 Ground |

| H2-3  | DIO1_CH2       | ISP Channel 2: Digital input/output 1        |

| H2-4  | DIO1_GND_CH2   | ISP Channel 2: Digital input/output 1 Ground |

| H2-5  | DIO2_CH2       | ISP Channel 2: Digital input/output 2        |

| H2-6  | DIO2_GND_CH2   | ISP Channel 2: Digital input/output 2 Ground |

| H2-7  | DIO3_CH2       | ISP Channel 2: Digital input/output 3        |

| H2-8  | DIO3_GND_CH2   | ISP Channel 2: Digital input/output 3 Ground |

| H2-9  | DIO4_CH2       | ISP Channel 2: Digital input/output 4        |

| H2-10 | DIO4_GND_CH2   | ISP Channel 2: Digital input/output 4 Ground |

| H2-11 | DIO5_CH2       | ISP Channel 2: Digital input/output 5        |

| H2-12 | DIO5_GND_CH2   | ISP Channel 2: Digital input/output 5 Ground |

| H2-13 | DIO6_CH2       | ISP Channel 2: Digital input/output 6        |

| H2-14 | DIO6_GND_CH2   | ISP Channel 2: Digital input/output 6 Ground |

| H2-15 | DIO7_CH2       | ISP Channel 2: Digital input/output 7        |

| H2-16 | DIO7_GND_CH2   | ISP Channel 2: Digital input/output 7 Ground |

| H2-17 | VPROG0_CH2     | ISP Channel 2: Programmable voltage 0        |

| H2-18 | VPROG0_GND_CH2 | ISP Channel 2: Programmable voltage 0 Ground |

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

| Ī | Pin#  | Signal Name    | Description                                  |  |

|---|-------|----------------|----------------------------------------------|--|

| Ī | H2-19 | VPROG1_CH2     | ISP Channel 2: Programmable voltage 1        |  |

| Ī | H2-20 | VPROG1_GND_CH2 | ISP Channel 2: Programmable voltage 1 Ground |  |

Table 11: Header Connector Signals Channel 3

| Pin#  | Signal Name    | Description                                  |

|-------|----------------|----------------------------------------------|

| н3-1  | DIO0_CH3       | ISP Channel 3: Digital input/output 0        |

| н3-2  | DIO0_GND_CH3   | ISP Channel 3: Digital input/output 0 Ground |

| н3-3  | DIO1_CH3       | ISP Channel 3: Digital input/output 1        |

| н3-4  | DIO1_GND_CH3   | ISP Channel 3: Digital input/output 1 Ground |

| н3-5  | DIO2_CH3       | ISP Channel 3: Digital input/output 2        |

| н3-6  | DIO2_GND_CH3   | ISP Channel 3: Digital input/output 2 Ground |

| н3-7  | DIO3_CH3       | ISP Channel 3: Digital input/output 3        |

| н3-8  | DIO3_GND_CH3   | ISP Channel 3: Digital input/output 3 Ground |

| н3-9  | DIO4_CH3       | ISP Channel 3: Digital input/output 4        |

| н3-10 | DIO4_GND_CH3   | ISP Channel 3: Digital input/output 4 Ground |

| Н3-11 | DIO5_CH3       | ISP Channel 3: Digital input/output 5        |

| Н3-12 | DIO5_GND_CH3   | ISP Channel 3: Digital input/output 5 Ground |

| н3-13 | DIO6_CH3       | ISP Channel 3: Digital input/output 6        |

| Н3-14 | DIO6_GND_CH3   | ISP Channel 3: Digital input/output 6 Ground |

| н3-15 | DIO7_CH3       | ISP Channel 3: Digital input/output 7        |

| Н3-16 | DIO7_GND_CH3   | ISP Channel 3: Digital input/output 7 Ground |

| н3-17 | VPROG0_CH3     | ISP Channel 3: Programmable voltage 0        |

| н3-18 | VPROG0_GND_CH3 | ISP Channel 3: Programmable voltage 0 Ground |

| н3-19 | VPROG1_CH3     | ISP Channel 3: Programmable voltage 1        |

| н3-20 | VPROG1_GND_CH3 | ISP Channel 3: Programmable voltage 1 Ground |

Table 12: Header Connector Signals Channel 4

| Pin#  | Signal Name  | Description                                  |

|-------|--------------|----------------------------------------------|

| H4-1  | DIO0_CH4     | ISP Channel 4: Digital input/output 0        |

| H4-2  | DIO0_GND_CH4 | ISP Channel 4: Digital input/output 0 Ground |

| H4-3  | DIO1_CH4     | ISP Channel 4: Digital input/output 1        |

| H4-4  | DIO1_GND_CH4 | ISP Channel 4: Digital input/output 1 Ground |

| H4-5  | DIO2_CH4     | ISP Channel 4: Digital input/output 2        |

| H4-6  | DIO2_GND_CH4 | ISP Channel 4: Digital input/output 2 Ground |

| H4-7  | DIO3_CH4     | ISP Channel 4: Digital input/output 3        |

| H4-8  | DIO3_GND_CH4 | ISP Channel 4: Digital input/output 3 Ground |

| H4-9  | DIO4_CH4     | ISP Channel 4: Digital input/output 4        |

| H4-10 | DIO4_GND_CH4 | ISP Channel 4: Digital input/output 4 Ground |

| H4-11 | DIO5_CH4     | ISP Channel 4: Digital input/output 5        |

| H4-12 | DIO5_GND_CH4 | ISP Channel 4: Digital input/output 5 Ground |

| H4-13 | DIO6_CH4     | ISP Channel 4: Digital input/output 6        |

YNERGY OF IN-SYSTEM PROGRAMMING I FADERS

| Pin#  | Signal Name    | Description                                  |

|-------|----------------|----------------------------------------------|

| H4-14 | DIO6_GND_CH4   | ISP Channel 4: Digital input/output 6 Ground |

| H4-15 | DIO7_CH4       | ISP Channel 4: Digital input/output 7        |

| H4-16 | DIO7_GND_CH4   | ISP Channel 4: Digital input/output 7 Ground |

| H4-17 | VPROG0_CH4     | ISP Channel 4: Programmable voltage 0        |

| H4-18 | VPROG0_GND_CH4 | ISP Channel 4: Programmable voltage 0 Ground |

| H4-19 | VPROG1_CH4     | ISP Channel 4: Programmable voltage 1        |

| H4-20 | VPROG1_GND_CH4 | ISP Channel 4: Programmable voltage 1 Ground |

Table 13: Aux Connectors

| Pin# | Signal Name | Description                                |

|------|-------------|--------------------------------------------|

| P2-1 | RLY_ON_CH1  | ISP Channel 1: Relay Barrier Driver Output |

| P2-2 | RLY_ON_CH2  | ISP Channel 2: Relay Barrier Driver Output |

| P2-3 | GND_RLY_CH1 | ISP Channel 1: Relay Barrier Ground        |

| P2-4 | GND_RLY_CH2 | ISP Channel 2: Relay Barrier Ground        |

| P2-5 | PWR_RLY_CH1 | ISP Channel 1: Relay Barrier Power Source  |

| P2-6 | PWR_RLY_CH2 | ISP Channel 2: Relay Barrier Power Source  |

|      |             |                                            |

| P1-1 | RLY_ON_CH3  | ISP Channel 3: Relay Barrier Driver Output |

| P1-2 | RLY_ON_CH4  | ISP Channel 4: Relay Barrier Driver Output |

| P1-3 | GND_RLY_CH3 | ISP Channel 3: Relay Barrier Ground        |

| P1-4 | GND_RLY_CH5 | ISP Channel 4: Relay Barrier Ground        |

| P1-5 | PWR_RLY_CH3 | ISP Channel 3: Relay Barrier Power Source  |

| P1-6 | PWR_RLY_CH4 | ISP Channel 4: Relay Barrier Power Source  |

Note: Aux connectors are intended to be used only as a development utility.

# **6 Technical Specifications**

#### 6.1 Absolute Maximum Ratings

Table 14: Absolute Maximum Ratings

| Parameter                                                  | Value        |

|------------------------------------------------------------|--------------|

| "POWER" Connector                                          |              |

| Supply voltage on line POWER (reference GND)               | +15V         |

| "ATE CONTROL" Connector                                    |              |

| Maximum input voltage on lines START, SEL[40], SG[10]      | -2V to +20V  |

| Maximum current on lines BUSY, PASS, FAIL                  | ±10mA        |

| "ISP GROUP" Connectors                                     |              |

| Maximum input voltage on lines DIO/AO[10], DIO[62], CLKOUT | -1V to +5.5V |

| Maximum current on lines DIO                               | ±24mA        |

| Maximum current on line VPROG0                             | 200 mA       |

| Maximum current on line VPROG1                             | 300 mA       |

|                                                            |              |

| "Relay Barrier"                                            |              |

| "Relay Barrier"  Coil Supply Voltage                       | 15V          |

|                                                            | 15V<br>3.3V  |

**Note:** Keep FlashRunner LAN 2.0 Next Generation always in a well-ventilated area in order to prevent product overheating, which could affect product performances and, if maintained for long time, it could damage product hardware components.

SYNERGY OF IN-SYSTEM PROGRAMMING LEADERS

Società Unipersonale

# 6.2 DC Characteristics and Functional Operating Range

Table 15: DC Characteristics and Functional Operating Range

| Parameter                                                       | Condition                                                                         |                       | Value |                       |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------|-------|-----------------------|

|                                                                 | -                                                                                 | Min                   | Тур   | Max                   |

| "ATE CONTROL" Connector                                         |                                                                                   |                       |       | -                     |

| V <sub>IL</sub> (input low voltage) on lines START, SEL[40]     |                                                                                   | 0V                    | -     | 0.8V                  |

| V <sub>IH</sub> (input high voltage) on lines START, SEL[40]    |                                                                                   | 2.4V                  | -     | 15V                   |

| V <sub>OL</sub> (output low voltage) on lines BUSY, FAIL, PASS  | I <sub>OL</sub> = 4mA                                                             | -                     | -     | V8.0                  |

| V <sub>OH</sub> (output high voltage) on lines BUSY, FAIL, PASS |                                                                                   | 4.5V                  | -     | 5V                    |

| "ISP" Connectors                                                |                                                                                   |                       |       |                       |

| V <sub>IL</sub> (input low voltage) on lines DIO                |                                                                                   | -                     | -     | 0.3V <sub>PROG0</sub> |

| V <sub>IH</sub> (input high voltage) on lines DIO               | Configured as digital lines                                                       | 0.7V <sub>PROG0</sub> | -     | $V_{PROG0}$           |

| Vol. (output low voltage) on lines DIO, CLKOUT                  | Configured as digital lines,<br>V <sub>PROG0</sub> = 3V, I <sub>OL</sub> = 12mA   | -                     | -     | 0.36V                 |

| V <sub>OH</sub> (output high voltage) on lines DIO, CLKOUT      | Configured as digital lines,<br>V <sub>PROG0</sub> = 3V, I <sub>OH</sub> = 12mA   | 2.56V                 | -     | -                     |

| V <sub>OL</sub> (output low voltage) on lines DIO, CLKOUT       | Configured as digital lines,<br>V <sub>PROG0</sub> = 5.5V, I <sub>OL</sub> = 24mA | -                     | -     | 0.36V                 |

| V <sub>OH</sub> (output high voltage) on lines DIO, CLKOUT      | Configured as digital lines,<br>V <sub>PROG0</sub> = 5.5V, I <sub>OH</sub> = 24mA | 4.86V                 | -     | -                     |

| I <sub>OH</sub> current (source) on lines DIO                   | Configured as input with active pull-ups                                          | -                     | 3.8mA | -                     |

| VPROG0 output voltage                                           |                                                                                   | 1.65V                 | -     | 5.5V                  |

| VPROG0 current (source)                                         |                                                                                   | -                     | -     | 200mA                 |

| VPROG1 output voltage                                           |                                                                                   | 6V                    | -     | 13.5V                 |

| VPROG1 current (source)                                         |                                                                                   | -                     | -     | 300mA                 |

| "POWER" Connector                                               |                                                                                   |                       |       |                       |

| Supply voltage                                                  |                                                                                   | 15V                   | -     | 15V                   |

| Power consumption                                               |                                                                                   | -                     | -     | 5A                    |

## 6.3 C Characteristics (TBW)

Table 16: AC Characteristics

| Parameter                                                                                    | ameter Condition             |                                        |      | Value |       |  |

|----------------------------------------------------------------------------------------------|------------------------------|----------------------------------------|------|-------|-------|--|

|                                                                                              | _                            |                                        | Min  | Тур   | Max   |  |

| trise on lines DIO[62],<br>DIO[10], CLKOUT when<br>configured as digital output<br>push-pull | V <sub>PROG0</sub> = 1.8V    | Load: 470Ω//100pF<br>(see figure 4.1a) | -    | 40ns  | -     |  |

|                                                                                              | $V_{PROG0} = 3.3V$           |                                        | -    | 30ns  | -     |  |

|                                                                                              | $V_{PROG0} = 5V$             |                                        | -    | 25ns  | -     |  |

| tFALL on lines DIO[62],<br>DIO[10], CLKOUT when<br>configured as digital output<br>push-pull | V <sub>PROG0</sub> = 1.8V    | Load: 470Ω//100pF<br>(see figure 4.1a) | -    | 35ns  | -     |  |

|                                                                                              | $V_{PROG0} = 3.3V$           |                                        | -    | 25ns  | -     |  |

|                                                                                              | V <sub>PROG0</sub> = 5V      |                                        | -    | 25ns  | -     |  |

|                                                                                              | V <sub>PROG1</sub> = 12V     |                                        | -    | 20µs  | -     |  |

|                                                                                              | V <sub>PROG1</sub> = 14.5V   |                                        | -    | 30µs  | -     |  |

| t <sub>RISE</sub> on line VPROG0                                                             | V <sub>PROG0</sub> = 0-1.8V  | Load: 15Ω//10mF (see figure 4.1a)      | -    | 10ms  | -     |  |

|                                                                                              | V <sub>PROG0</sub> = 0-3.3V  | Load: 22Ω//10mF (see figure 4.1a)      | -    | 15ms  | -     |  |

|                                                                                              | V <sub>PROG0</sub> = 0-5.5V  | Load: 22Ω//10mF (see figure 4.1a)      | -    | 20ms  | -     |  |

| t <sub>FALL</sub> on line VPROG0                                                             | V <sub>PROG0</sub> = 1.8-0V  | Load: 10mF (see figure 41b)            | -    | 300ms | -     |  |

|                                                                                              | V <sub>PROG0</sub> = 3.3-0V  |                                        | -    | 350ms | -     |  |

|                                                                                              | V <sub>PROG0</sub> = 5.5-0V  |                                        | -    | 350ms | -     |  |

| t <sub>RISE</sub> on line VPROG1                                                             | V <sub>PROG1</sub> = 0-3V    | Load: 10Ω//1mF (see figure 4.1a)       | -    | 1.3ms | -     |  |

|                                                                                              | $V_{PROG1} = 0-5V$           | Load: 47Ω//1mF (see figure 4.1a)       | -    | 1.8ms | -     |  |

|                                                                                              | V <sub>PROG1</sub> = 0-14.5V | Load: 94Ω//1mF (see figure 4.1a)       | -    | 13ms  | -     |  |

| t <sub>FALL</sub> on line VPROG1                                                             | V <sub>PROG1</sub> = 3-0V    | Load: 1mF (see figure 4.1b)            | -    | 18ms  | -     |  |

|                                                                                              | V <sub>PROG1</sub> = 5-0V    |                                        | -    | 30ms  | -     |  |

|                                                                                              | V <sub>PROG1</sub> = 14.5-0V |                                        | -    | 45ms  | -     |  |

| CLKOUT frequency                                                                             |                              |                                        | 0MHz | -     | 25MHz |  |

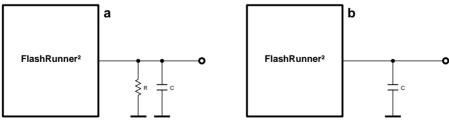

Figure 15: Load Conditions

YNERGY OF IN-SYSTEM PROGRAMMING LEADERS

## 6.4 Physical and Environmental Specifications

Table 17: Physical and Environmental Specifications

| Parameter                      | Value                                            |

|--------------------------------|--------------------------------------------------|

| Dimensions, open frame version | 140 x 60 x 18 mm                                 |

| Dimensions, case version       | 140 x 70 x 18 mm                                 |

| Dimensions, with relay barrier | -                                                |

| "ISP" connectors type          | 48 way, 3 row, DIN 41612, pitch = 2.54mm (male)  |

| "ATE CONTROL" connector type   | 14 way, 2 row, box header, pitch = 1.27mm (male) |

| "USB" connector type           | USB-B micro receptable                           |

| "LAN" connector type           | RJ-45 connector                                  |

| "POWER" connector type         | DC Plug                                          |

| Operating temperature          | 0-50°C                                           |

| Operating humidity             | 90% max (without condensation)                   |

| Storage temperature            | 0-70°C                                           |

| Storage humidity               | 90% max (without condensation)                   |

| EMC (EMI/EMS)                  | CE, FCC                                          |

| Sd card size                   | Up to 200 GB, by default mounts 2GB              |

|                                |                                                  |